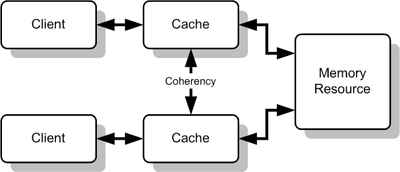

Cache może być użyty w celu poprawy wydajności dostępu do danego zasobu. Gdy istnieje kilka takich cache'ów dla tego samego zasobu, jak pokazano na rysunku, może to prowadzić do problemów. Spójność pamięci podręcznej lub koherencja pamięci podręcznej odnosi się do wielu sposobów upewnienia się, że wszystkie pamięci podręczne zasobu mają te same dane, oraz że dane w pamięci podręcznej mają sens (nazywane integralnością danych). Spójność pamięci podręcznej jest specjalnym przypadkiem spójności pamięci.

Mogą wystąpić problemy, jeśli istnieje wiele pamięci podręcznych wspólnego zasobu pamięci, ponieważ dane w pamięci podręcznej mogą nie mieć już sensu, lub jedna pamięć podręczna może nie mieć już tych samych danych, co inne. Częstym przypadkiem, w którym pojawia się ten problem, jest pamięć podręczna procesorów w systemie wieloprocesorowym. Jak widać na rysunku, jeśli górny klient ma kopię bloku pamięci z poprzedniego odczytu, a dolny klient zmienia ten blok pamięci, górny klient może zostać pozostawiony z nieprawidłową pamięcią podręczną pamięci, nie wiedząc o tym. Koherencja pamięci podręcznej ma za zadanie zarządzać takimi konfliktami i utrzymywać spójność pomiędzy pamięcią podręczną a pamięcią.

Dlaczego koherencja pamięci podręcznej jest ważna?

W systemach z wieloma jednostkami wykonawczymi (rdzeniami, CPU, węzłami) brak koherencji prowadzi do błędów trudnych do wykrycia: programy mogą operować na przestarzałych danych, występują niespójne wyniki odczytów i zapisów, a debugowanie takich problemów jest kosztowne. Koherencja jest więc kluczowa dla poprawności programów równoległych i wydajności systemu.

Typowe problemy i ich przyczyny

- Dane nieaktualne (stale data): jeden cache ma starą kopię, podczas gdy inny zapisał nowe wartości.

- Wyścigi zapisu/odczytu: brak synchronizacji między wątkami może spowodować odczytanie częściowo zmodyfikowanych danych.

- Fałszywe współdzielenie (false sharing): dwie zmienne niezależne znajdują się w tej samej linii cache; zmiana jednej powoduje niepotrzebne unieważnienia drugiej, obniżając wydajność.

- Skalowalność: mechanizmy koherencji mogą wymagać dużej przepustowości magistrali lub znaczącej pamięci pomocniczej (np. katalogów), co utrudnia skalowanie do dużej liczby węzłów.

- Koszt i opóźnienia: utrzymywanie koherencji generuje dodatkowy ruch sieciowy/magistralowy i opóźnienia reakcji na operacje pamięci.

Główne mechanizmy rozwiązujące problem

Poniżej najczęściej stosowane podejścia stosowane zarówno w sprzęcie, jak i w oprogramowaniu:

- Protokoły snooping (nasłuchowe): każdy cache „nasłuchuje” operacje innych cache'y na wspólnej magistrali i reaguje (np. unieważnia swoją kopię). Przykładowe schematy: MSI, MESI, MOESI.

- Write-invalidate vs write-update:

- Write-invalidate — zapis powoduje unieważnienie kopii w innych cache'ach; najczęściej używane, zmniejsza ruch, gdy następuje wiele zapisów.

- Write-update — zapis propaguje nową wartość do innych cache'ów; może być użyteczne przy częstych odczytach po zapisie, ale generuje więcej ruchu.

- Directory-based coherence: zamiast globalnego nasłuchiwania, utrzymuje się katalog (directory) informujący, które węzły mają kopie danej linii — redukuje nadmiarowy ruch i poprawia skalowalność w dużych systemach rozproszonych.

- Write-through vs write-back: polityki zapisu wpływają na koherencję. Write-through natychmiast aktualizuje pamięć główną, ułatwiając spójność, ale zwiększa ruch; write-back aktualizuje pamięć główną później, co jest bardziej wydajne, ale wymaga mechanizmów koordynacji między cache'ami.

- Synchronizacja programowa: bariery pamięciowe, instrukcje atomiczne i mechanizmy blokad pomagają gwarantować spójne widoki pamięci w kontekście modeli pamięci (np. sequential consistency vs. relaxed models).

- Strategie w systemach rozproszonych/HTTP: w kontekście cache'ów webowych używa się TTL, mechanizmów unieważniania (purge), walidacji (ETag, Last-Modified) i protokołów do zapewnienia spójności między cache'ami i źródłem.

Protokół MESI — przykład praktyczny

MESI to popularny protokół koherencji z czterema stanami linii cache: Modified, Exclusive, Shared, Invalid. Pozwala on kontrolować, kiedy linia może być modyfikowana lokalnie oraz kiedy trzeba powiadomić/unieważnić kopie w innych cache'ach. Dzięki temu zmniejsza się liczba niepotrzebnych operacji I/O i poprawia wydajność przy jednoczesnym zachowaniu spójności.

Strategie ograniczania kosztów i błędów

- Unikać false sharing przez odpowiednie wyrównanie i padding struktury danych.

- Stosować lokalne buforowanie i ograniczać wspólne zmienne tam, gdzie to możliwe (np. używanie thread-local storage).

- Zgrupować operacje zapisu tak, by zmniejszyć liczbę unieważnień lub aktualizacji rozgłaszanych do innych cache'ów.

- W wybieralnych aplikacjach rozproszonych rozważyć modele spójności słabsze niż silna spójność (np. eventual consistency) jeżeli wymagania poprawności na to pozwalają—to zmniejsza koszty utrzymania koherencji kosztem prostoty programowania.

Koherencja vs. spójność pamięci

Warto rozróżnić pojęcia: koherencja pamięci podręcznej dotyczy tego, czy różne kopie tej samej lokalizacji pamięci są aktualizowane i widoczne w przewidywalny sposób. Spójność pamięci (memory consistency) to model określający kolejność, w jakiej obserwowane są operacje pamięci (np. czy zapis A musi być widoczny przed odczytem B). Koherencja jest zwykle potrzebna, ale sama w sobie nie gwarantuje wszystkich właściwości modelu pamięci wymaganych przez programy równoległe.

Podsumowanie — najważniejsze punkty

- Koherencja pamięci podręcznej zapewnia, że kopie tych samych danych w różnych cache'ach pozostają sensowne i spójne.

- Problemy obejmują dane nieaktualne, wyścigi, fałszywe współdzielenie i narzut komunikacyjny.

- Rozwiązania obejmują protokoły nasłuchowe (MSI/MESI), systemy oparte na katalogach, polityki zapisu (write-through/write-back) oraz synchronizację programową.

- Wybór mechanizmu to kompromis między poprawnością, wydajnością i skalowalnością; projektanci systemów dobierają rozwiązania w zależności od wymagań aplikacji i architektury sprzętowej.

Praktyczna wskazówka: podczas projektowania oprogramowania wielowątkowego sprawdzaj, czy dane współdzielone rzeczywiście muszą być współdzielone; minimalizacja współdzielenia i unikanie fałszywego współdzielenia często daje największe korzyści wydajnościowe przy jednoczesnym zmniejszeniu złożoności mechanizmów koherencji.